BeagleBoard.org Foundation Mar 08, 2023

# **Table of contents**

# **Chapter 1**

# Introduction

Welcome to the BeagleBoard documentation project. If you are looking for help with your Beagle open-hardware development platform, you've found the right place!

**Important:** This documentation is a work in progress. For the latest versions of this documentation, be sure to check the official release sites:

- https://docs.beagle.cc (cached with local proxies)

- https://docs.beagleboard.org (non-cached, without proxies)

For bleeding edge (development-stage) documentation:

https://docs.beagleboard.io (straight from docs repo)

Please check out our *Support* page to find out how to get started, resolve issues, and engage with the developer community. Don't forget that this is an open-source project! Your contributions are welcome. Learn about how to contribute to the BeagleBoard documentation project and any of the many open-source Beagle projects ongoing on our *Contribution* page.

**Warning:** Make sure you thoroughly read and agree with our *Terms & Conditions* which covers warnings, restrictions, disclaimers, and warranty for all of our boards. Use of either the boards or the design materials constitutes agreement to the T&C including any modifications done to the hardware or software solutions provided by beagleboard.org foundation.

# 1.1 Support

## 1.1.1 Getting started

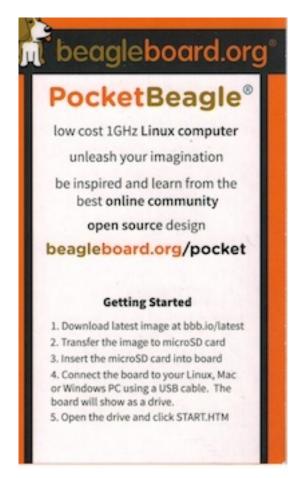

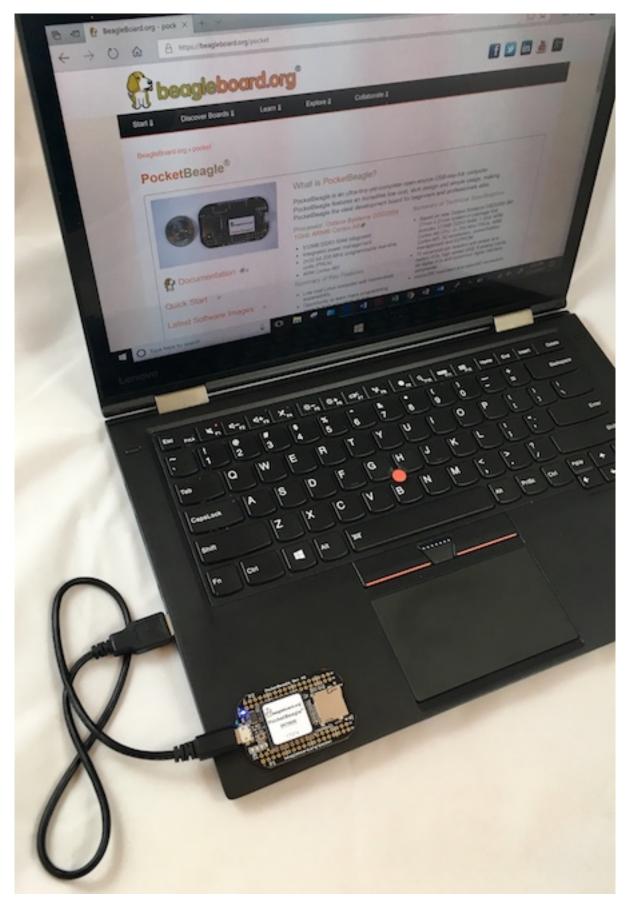

The starting experience for all Beagles has been made to be as consistent as is possible. For any of the Beagle Linux-based open hardware computers, visit *Getting Started Guide*.

### **Getting Started Guide**

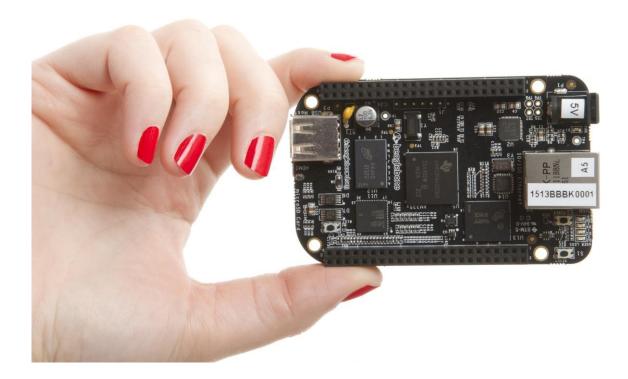

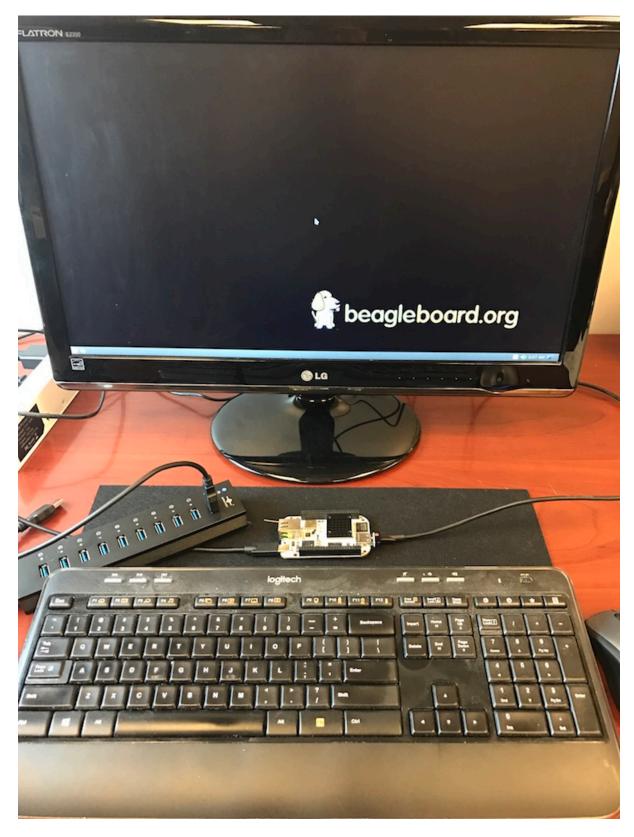

Beagles are tiny computers ideal for learning and prototyping with electronics. Read the step-by-step getting started tutorial below to begin developing with your Beagle in minutes.

Update board with latest software This step may or may not be necessary, depending on how old a software image you already have, but executing this step, the longest step, will ensure the rest will go as smooth as possible.

Download the latest software image Download the latest software image from beagleboard.org distros page. The "IoT" images provide more free disk space if you don't need to use a graphical user interface (GUI).

**Note:** Due to sizing necessities, this download may take 30 minutes or more.

The Debian/Ubuntu distribution is provided for the boards. The file you download will have an .img.xz extension. This is a compressed sector-by-sector image of the SD card.

| orete Leern Getting Started Boards Mission                                                                                                                                                                                                                                                                                                      |                                                                                                                                                    |                                                                                                                                                       | ۹ 🎯 ۲ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Latest Firmware Images                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                    |                                                                                                                                                       |       |

| Home + Latest Firmware Images                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                    |                                                                                                                                                       |       |

| Deveload the kitest Immare for your Beoglebourd, Beoglebourd 44, Baog<br>Beoglebon Bas, SectoRibuth Beoglebourd Genes, SectoRula Heoglebo<br>Beoglebon Bas, Katelland, and Beoglebo Bask Astalandi. Marton E<br>See the Geting Stand Glade for Initia on loading these majors. See our D<br>PRes Software Distributions [Science Fritter Cystom | we Green Wireless, SeeedStudio Bengletione Gre<br>BengleBone uSomiQ, Neuromeka Bengletione Air,<br>ebian page on how the latest images are built.  | en Geteway, SanCloud BeagleBone Enhanced, element14                                                                                                   |       |

| BeegleBone AH64 Edge AI Debian distro image EDGEAI<br>version used in webinar demo. Debian im<br>arm64/e67                                                                                                                                                                                                                                      | Debian 11.5 2022 11.01 10:08 50 X/CC<br>age for BengleBone Al-64 Kernet 5.0120-6-<br>U Sock bashel V 2021 01 default<br>passend is (debian2emppwd) | AM355 Decem 10.3 2020 O4 06 4058 eMAC lot<br>Planter<br>Brater InZ Method, preprince denistry for Bengletone<br>on board eMAC facility via monSD card |       |

| <b>≜(mgge ≜156250</b> 2023-0110                                                                                                                                                                                                                                                                                                                 | <b>≜ thu256</b> 2022-11-15                                                                                                                         | <b>≜</b> trage <b>≜</b> sha256 2020-04-06                                                                                                             |       |

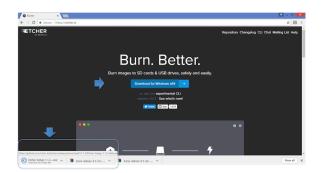

Install SD card programming utility Download and install balenaEtcher.

| SelenaEtther - Home X +                                                                                                                                      |                                   |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------|

| ← → C iii https://www.balena.lo/etcher/                                                                                                                      |                                   | x 🔩 o Q |

| An open source project by 🌍 bailena   More producte \vee                                                                                                     | <b>9</b>                          |         |

|                                                                                                                                                              |                                   |         |

| Source Forum M                                                                                                                                               | telling list Changelog Etcher Pro |         |

|                                                                                                                                                              |                                   |         |

|                                                                                                                                                              |                                   |         |

| Electric Electrica                                                                                                                                           |                                   |         |

| Flash. Flawless.                                                                                                                                             |                                   |         |

|                                                                                                                                                              |                                   |         |

| Flash OS images to SD cards & USB drives, safely and easily.                                                                                                 |                                   |         |

|                                                                                                                                                              |                                   |         |

|                                                                                                                                                              |                                   |         |

| $\oplus \longrightarrow \blacksquare \longrightarrow \forall$                                                                                                |                                   |         |

| Select image Select drive Flash                                                                                                                              |                                   |         |

|                                                                                                                                                              |                                   |         |

|                                                                                                                                                              |                                   |         |

| Download for macO5                                                                                                                                           |                                   |         |

|                                                                                                                                                              |                                   |         |

| Etcher for Windows (x86)x64) (installer)                                                                                                                     |                                   |         |

| Etcher for Windows (x86)x64) (Portable)                                                                                                                      |                                   |         |

| Etcher for Linux x64 (64-bit) (AppImage)                                                                                                                     |                                   |         |

| Etcher for Linux x86 (32-bit) (AppImage)                                                                                                                     |                                   |         |

|                                                                                                                                                              |                                   |         |

|                                                                                                                                                              |                                   |         |

| Validated Flashing V Hard Drive Friendly FEATURES                                                                                                            |                                   |         |

| No more writing images on competed Askes drive selection obvious to avoid cards and wondering why your device wiping your entire hard-drive Abetter way to b | urn.                              |         |

| inst bootion.                                                                                                                                                |                                   |         |

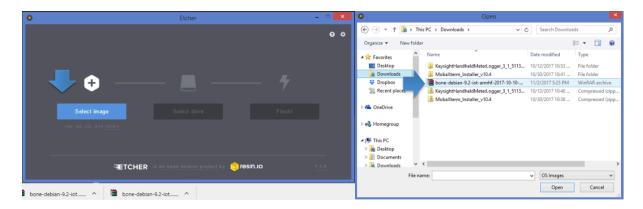

**Connect SD card to your computer** Use your computer's SD slot or a USB adapter to connect the SD card to your computer.

| •                  |                    | 0 ¢    |

|--------------------|--------------------|--------|

| <b>.</b> —         |                    | _ 4    |

| bone-debi7-4gb.img | Generic SICE Media | Flash! |

| Change             |                    |        |

|                    |                    |        |

**Write the image to your SD card** Use Etcher to write the image to your SD card. Etcher will transparently decompress the image on-the-fly before writing it to the SD card.

**Eject the SD card** Eject the newly programmed SD card.

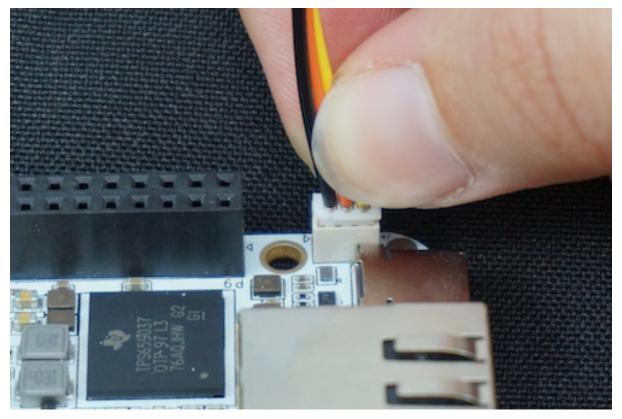

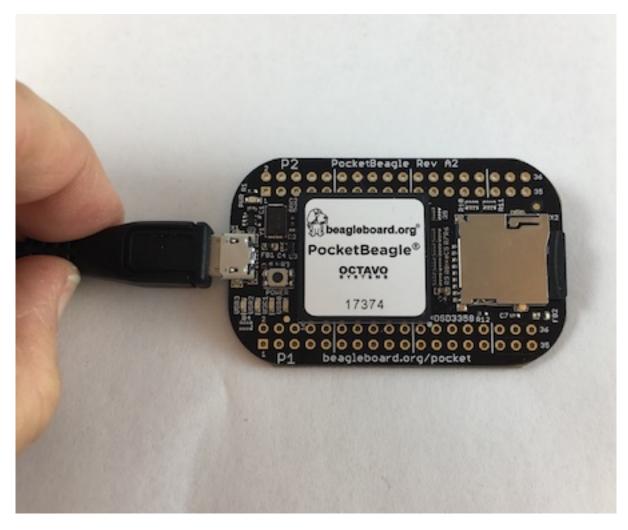

**Boot your board off of the SD card** Insert SD card into your (powered-down) board, hold down the USER/BOOT button and apply power, either by the USB cable or 5V adapter.

If using an original BeagleBone or PocketBeagle, you are done.

**Note:** If using BeagleBone Black, BeagleBone Blue, BeagleBone AI, BeagleBone AI-64, BeaglePlay or other board with on-board eMMC flash and you desire to write the image to your on-board eMMC, you'll need to

follow the instructions at http://elinux.org/Beagleboard:BeagleBoneBlack\_Debian#Flashing\_eMMC. When the flashing is complete, all 4 USRx LEDs will be steady off and possibly power down the board upon completion. This can take up to 45 minutes. Power-down your board, remove the SD card and apply power again to finish.

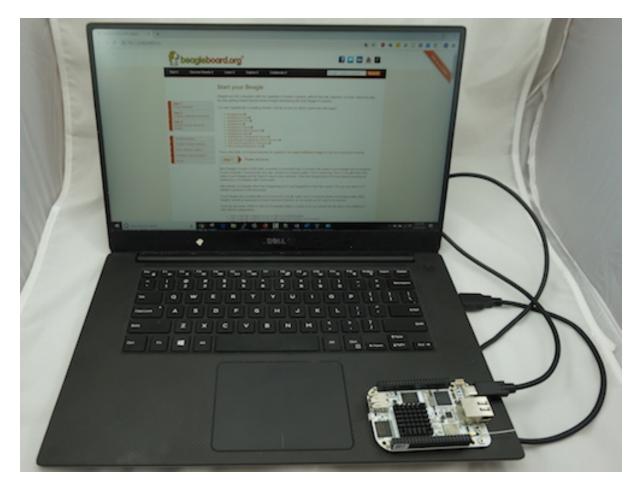

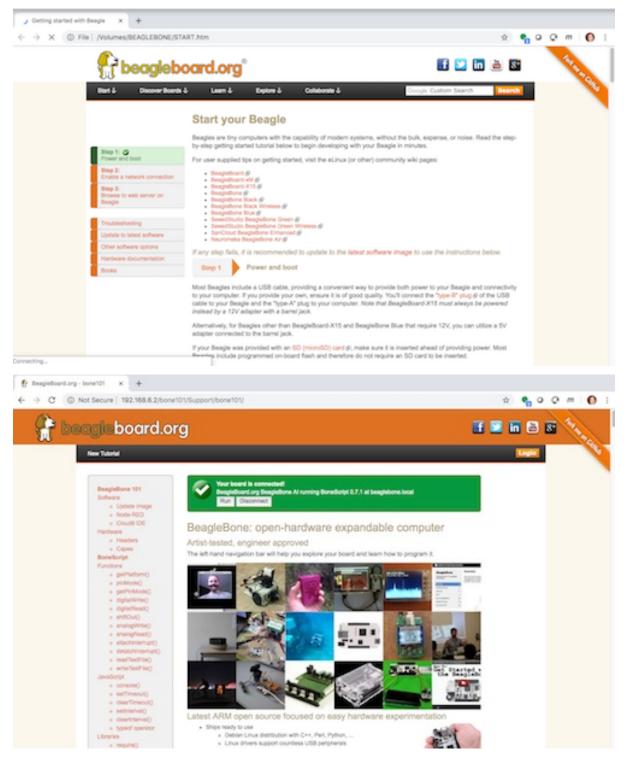

**Start your Beagle** If any step fails, it is recommended to update to the latest software image using the instructions above.

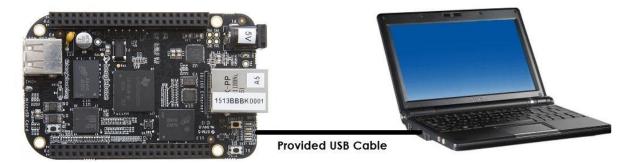

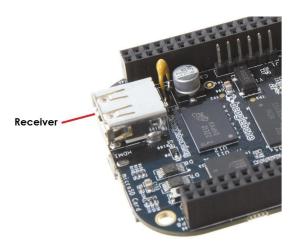

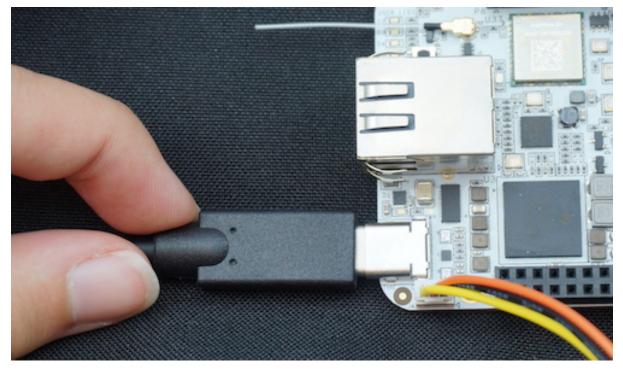

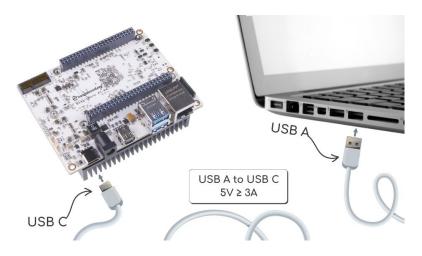

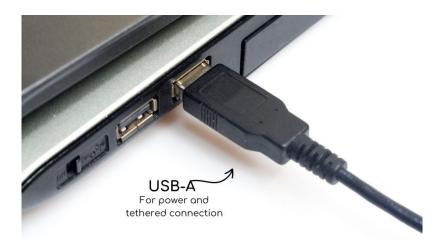

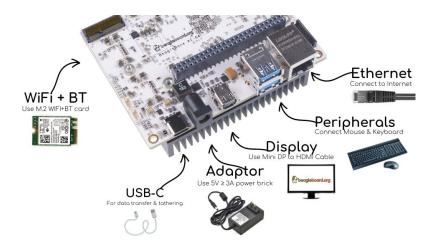

**Power and boot** Most Beagles can be powered via a USB cable, providing a convenient way to provide both power to your Beagle and connectivity to your computer. Be sure the cable is of good quality and your source can provide enough power.

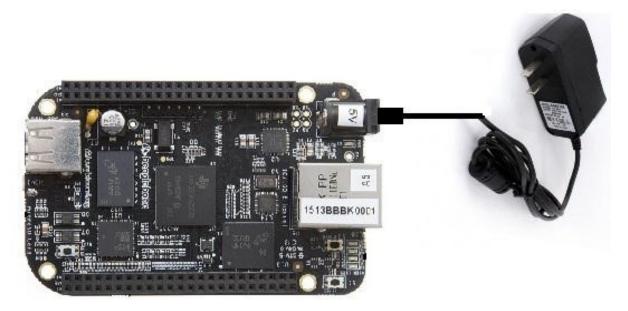

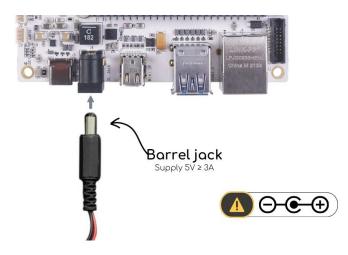

Alternatively, your Beagle may have a barrel jack which can take power from a wall adapter. Checkout *Power supplies* to get the correct adapter for your Beagle.

**Danger:** Make sure to use only a 5V center positive adapter for all Beagles except BeagleBone Blue and BeagleBoard-X15 (12V).

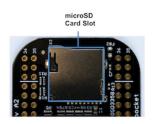

If you are using your Beagle with an SD (microSD) card, make sure it is inserted ahead of providing power. Most Beagles include programmed on-board flash and therefore do not require an SD card to be inserted.

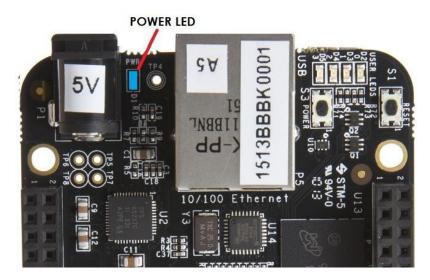

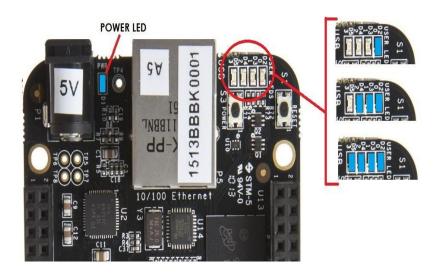

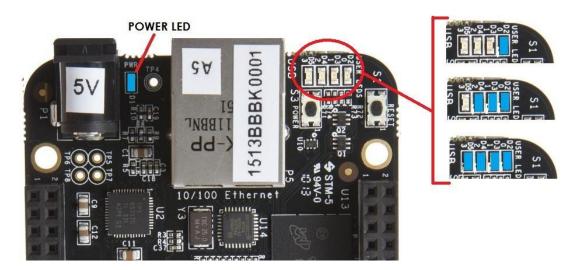

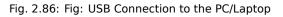

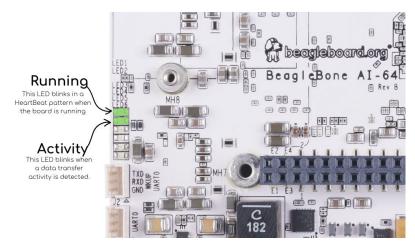

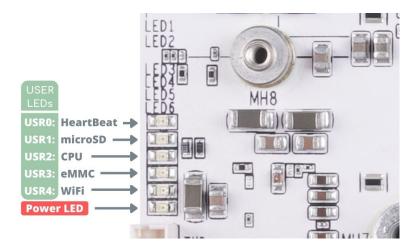

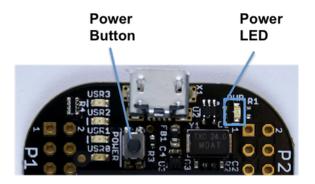

You'll see the power (PWR or ON) LED lit steadily. Within a minute or so, you should see the other LEDs blinking in their default configurations. Consult your *Boards* documentation to locate these LEDs.

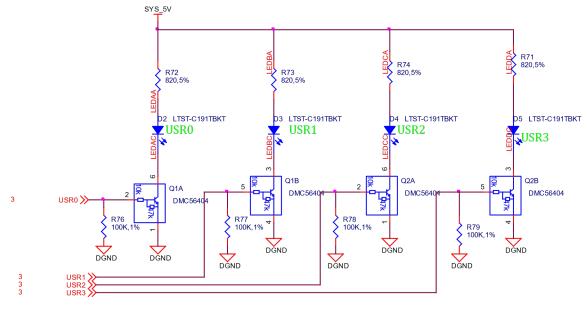

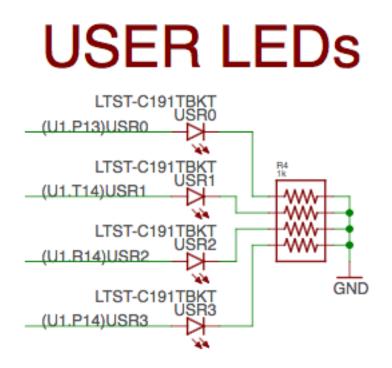

- USR0 is typically configured at boot to blink in a heartbeat pattern.

- USR1 is typically configured at boot to light during SD (microSD) card accesses.

- USR2 is typically configured at boot to light during CPU activity.

- USR3 is typically configured at boot to light during eMMC accesses.

- USR4/WIFI is typically configured at boot to light with WiFi (client) network association (Only on boards with built-in WiFi or M.2).

**Enable a network connection** If connected via USB, a network adapter should show up on your computer. Your Beagle should be running a DHCP server that will provide your computer with an IP address of either 192.168.7.1 or 192.168.6.1, depending on the type of USB network adapter supported by your computer's operating system. Your Beagle will reserve 192.168.7.2 or 192.168.6.2 for itself.

If your Beagle includes WiFi, an access point called "BeagleBone-XXXX" where "XXXX" varies between boards. The access point password defaults to "BeagleBone". Your Beagle should be running a DHCP server that will provide your computer with an IP address in the 192.168.8.x range and reserve 192.168.8.1 for itself.

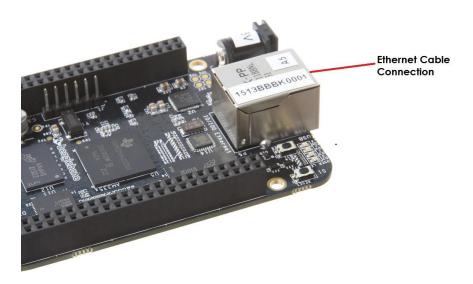

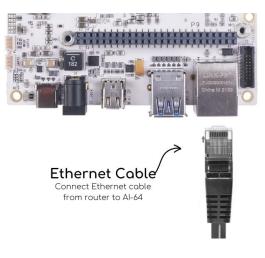

If your Beagle is connected to your local area network (LAN) via either Ethernet or WiFi, it will utilize mDNS to broadcast itself to your computer. If your computer supports mDNS, you should see your Beagle as beaglebone.local. Non-BeagleBone boards will utilize alternate names. Multiple BeagleBone boards on the same network will add a suffix such as beaglebone-2.local.

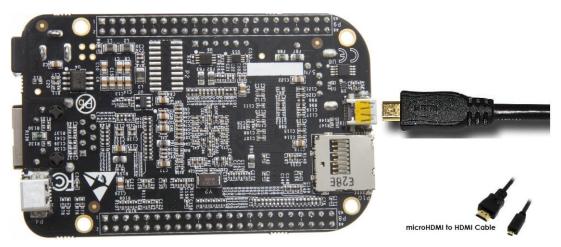

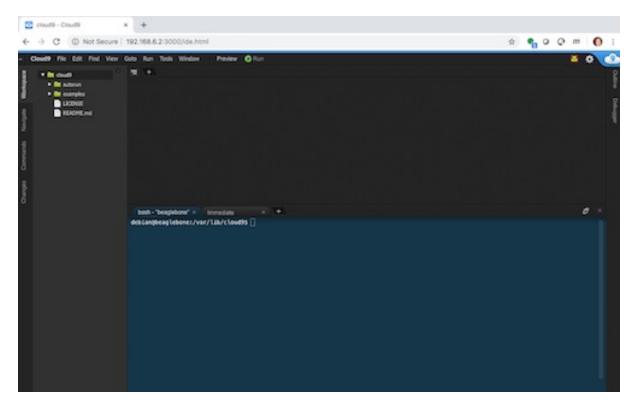

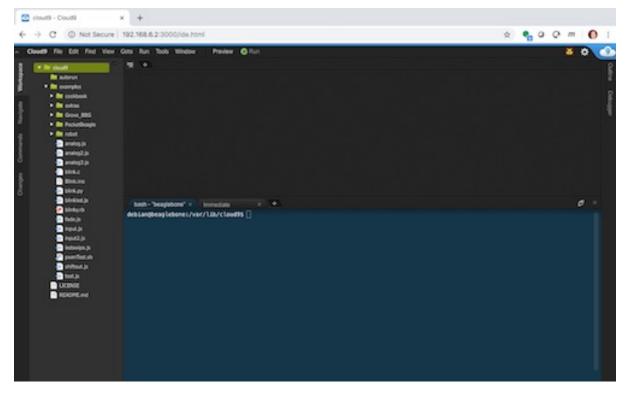

**Browse to your Beagle** A web server with an Visual Studio Code (IDE) should be running on your Beagle. Point your browser to **http://192.168.7.2:3000** to begin development.

**Note:** Use either Firefox or Chrome (Internet Explorer will NOT work), browse to the web server running on your board. It will load a presentation showing you the capabilities of the board. Use the arrow keys on your keyboard to navigate the presentation.

The below table summarizes the typical addresses.

| Link                      | Connection type | Operating System(s) |

|---------------------------|-----------------|---------------------|

| http://192.168.7.2        | USB             | Windows             |

| http://192.168.6.2        | USB             | Mac OS X, Linux     |

| http://192.168.8.1        | WiFi            | all                 |

| http://beaglebone.local   | all             | mDNS enabled        |

| http://beaglebone-2.local | all             | mDNS enabled        |

#### Troubleshooting Do not use Internet Explorer.

Virtual machines are not recommended when using the direct USB connection. It is recommended you use only network connections to your board if you are using a virtual machine.

When using 'ssh' with the provided image, the username is 'debian' and the password is 'temppwd'.

With the latest images, it should no longer be necessary to install drivers for your operating system to give you network-over-USB access to your Beagle. In case you are running an older image, an older operating system or need additional drivers for serial access to older boards, links to the old drivers are below.

| Operating system | USB Driver       | Comments                                                                         |

|------------------|------------------|----------------------------------------------------------------------------------|

| Windows (64-bit) | 64-bit installer | If in doubt, try the 64-bit installer first.                                     |

| Windows (32-bit) | 32-bit installer |                                                                                  |

| Mac OS X         | Network Serial   | Install both sets of drivers.                                                    |

| Linux            | mkudevrules.sh   | Driver installation isn't required, but you might find a few udev rules helpful. |

Note: For Windows (64-bit):

- 1. Windows Driver Certification warning may pop up two or three times. Click "Ignore", "Install" or "Run".

- 2. To check if you're running 32 or 64-bit Windows see this.

- 3. On systems without the latest service release, you may get an error (0xc000007b). In that case, please perform the following and retry: https://answers.microsoft.com/en-us/windows/forum/all/ windows-10-error-code-0xc000007b/02b74e7d-ce19-4ba4-90f0-e16e8d911866

- 4. You may need to reboot Windows.

- 5. These drivers have been tested to work up to Windows 10

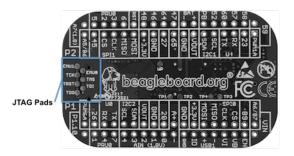

Additional FTDI USB to serial/JTAG information and drivers are available from https://www.ftdichip.com/Drivers/ VCP.htm

Additional USB to virtual Ethernet information and drivers are available from http://www.linux-usb.org/gadget/ and https://joshuawise.com/horndis

Visit https://docs.beagleboard.org/latest/intro/support/index.html for additional debugging tips.

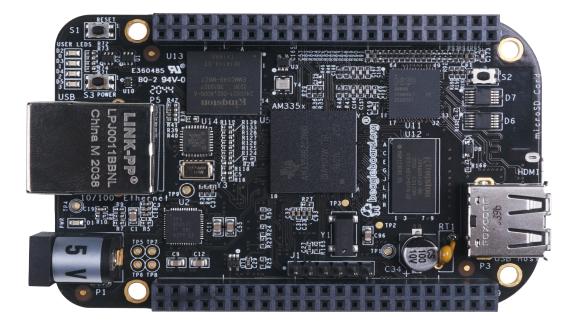

**Hardware documentation** Be sure to check check the latest hardware documentation for your board at https://docs.beagleboard.org. Detailed design materials for various boards can be found at https://git. beagleboard.org/explore/projects/topics/boards.

Books For a complete list of books on BeagleBone, see beagleboard.org/books.

Bad to the Bone

Perfect for high-school seniors or freshman university level text, consider using "Bad to the Bone"

#### BeagleBone Cookbook

A lighter treatment suitable for a bit broader audience without the backgrounders on programming and electronics, consider "BeagleBone Cookbook"

Exploring BeagleBone and Embedded Linux Primer

To take things to the next level of detail, consider "Exploring BeagleBone" which can be considered the missing software manual and utilize "Embedded Linux Primer" as a companion textbook to provide a strong base on embedded Linux suitable for working with any hardware that will run Linux.

### 1.1.2 Getting support

BeagleBoard.org products and open hardware designs are supported via the on-line community resources. We are very confident in our community's ability to provide useful answers in a timely manner. If you don't get a productive response within 24 hours, please escalate issues to Jason Kridner (contact info available on the About Page). In case it is needed, Jason will help escalate issues to suppliers, manufacturers or others. Be sure to provide a link to your questions on the community forums as answers will be provided there.

Be sure to ask smart questions that provide the following:

- What are you trying to accomplish?

- What did you find when researching how to accomplish it?

- · What are the detailed results of what you tried?

- · How did these results differ from what you expected?

- What would you consider to be a success?

**Important:** Remember that community developers are volunteering their expertise. Respect developers time and expertise and they might be happy to share with you. If you want paid support, there are *Consulting and other resources* options for that.

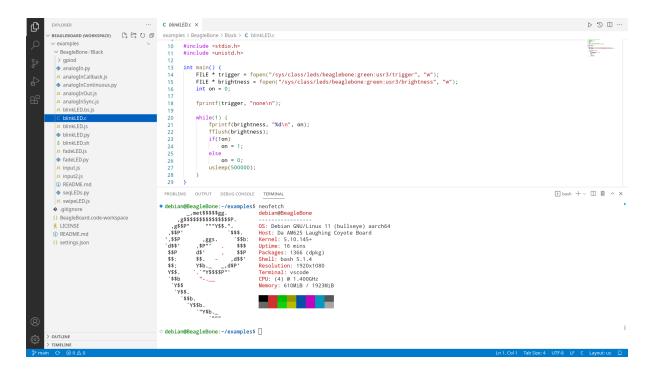

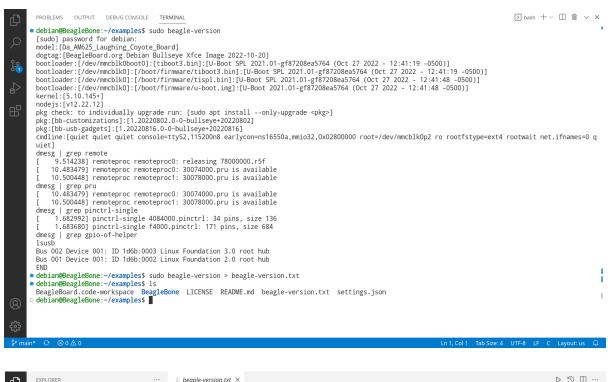

#### **Diagnostic tools**

Best to be prepared with good diagnostic information to aide with support.

- · Output of beagle-version script needed for support requests

- Beagle Tester source

|                                                                                                        | $\equiv$ beagle-version.txt $	imes$                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| :)                                                                                                     | examples > ≡ beagle-v                                                                                                                                                                                                                                        | /ersion.txt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ly.                                                                                                    |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Delta Marcalante                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Run Code<br>Open to the Side<br>Open With<br>Open in Integrated<br>Select for Compare<br>Open Timeline | Ctrl+Alt+N<br>Ctrl+Enter<br>Terminal                                                                                                                                                                                                                         | <pre>\eBoard.org Debian Bullseye Xfce Image 2022-10-20]<br/>'dev/mmcblk0boot0]:[tiboot3.bin]:[U-Boot SPL 2021.01-gf87208ea5764<br/>'dev/mmcblk0]:[/boot/firmware/tiboot3.bin]:[U-Boot SPL 2021.01-gf872<br/>'dev/mmcblk0]:[/boot/firmware/tispl.bin]:[U-Boot SPL 2021.01-gf87208'<br/>'dev/mmcblk0]:[/boot/firmware/u-boot.img]:[U-Boot 2021.01-gf87208'<br/>'dev/mmcblk0]:[/boot/firmware/u-boot.img]:[U-Boot 2021.01-gf87208'<br/>'dev/mmcblk0]:[/boot/firmware/u-boot.img]:[U-Boot SPL 2021.01-gf87208'<br/>'mizition]:[/boot/firmware/u-boot.img]:[U-Boot SPL 2021.01-gf87208'<br/>'mizition]:[/boot/firmware/u-boot.img]:[U-Boot SPL 2021.01-gf87208'<br/>'mizition]:[/boot/firmware/u-boot.img]:[/boot SPL 2021.01-gf87208'<br/>'mizition]:[/boot/firmware/u-boot.img]:[/boot SPL 20220802]<br/>'adget5]:[/boot/firmware/u-boot.img]:[/boot SPL 20220816]</pre> | 208ea5764 (Oct<br>8ea5764 (Oct 2<br>5764 (Oct 27 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Cut<br>Copy                                                                                            | Ctrl+X<br>Ctrl+C                                                                                                                                                                                                                                             | EBUG CONSOLE TERMINAL<br>]:[1.20220816.0-0-bullseye+20220816]<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <pre>▷ bash + ~ □ □ ^ &gt;<br/>t=/dev/mmcblk0p2 ro ro</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Copy Path<br>Copy Relative Path                                                                        | Ctrl+Alt+C<br>Ctrl+Shift+Alt+C                                                                                                                                                                                                                               | teproc remoteproc0: releasing 78000000.r5f<br>teproc remoteproc0: 30074000.pru is available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Rename<br>Delete Permanently                                                                           | F2<br>Delete                                                                                                                                                                                                                                                 | teproc remoteproc0: 30074000.pru is available<br>teproc remoteproc1: 30078000.pru is available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Git: View File History                                                                                 | , 1.0020003 bri                                                                                                                                                                                                                                              | trl-single 4084000.pinctrl: 34 pins, size 136<br>Ltrl-single f4000.pinctrl: 171 pins, size 684                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                        | lsusb<br>Bus 002 Device 001<br>Bus 001 Device 001<br>END<br>debian@BeagleBone:<br>debian@BeagleBone:<br>BeagleBoard.code-w                                                                                                                                   | : ID 1d6b:0003 Linux Foundation 3.0 root hub<br>: ID 1d6b:0002 Linux Foundation 2.0 root hub<br>~/examples\$ sudo beagle-version > beagle-version.txt<br>~/examples\$ ls<br>orkspace BeagleBone LICENSE README.md beagle-version.txt settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | json                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                        | La Code<br>Open to the Side<br>Open to the Side<br>Open With<br>Open In Integrated<br>Select for Compare<br>Open Timeline<br>Copy Path<br>Copy Path<br>Copy Path<br>Copy Path<br>Copy Relative Path<br>Rename<br>Delete Permanently<br>Cit: View File Histor | examples > E beagle-4<br>1 model:[Da_A<br>Run Code     Ctrl+Alt+N<br>Open to the Side       Open to the Side     Ctrl+Enter<br>Open With<br>Open in Integrated Terminal       Select for Compare     Ctrl-Xither<br>Open Timeline       Cut     Ctrl+Xither<br>Copy       Cut     Ctrl+Xither<br>Open Timeline       Cut     Ctrl+Xither<br>Copy       Download     Ctrl+Shift+Alt+C       Copy Relative Path     Ctrl+Shift+Alt+C       Cepte Permanently     Delete       Git: View File History     Alt+H       rkspace     gesg1 grep gpio-<br>Isusb       Bus 002 Device 001<br>Bus 001 Device 001<br>END       • debian@BeagleBone:<br>• debian@BeagleBone:<br>• debian@BeagleBone:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | examples > E beagle-version.txt         1       model:[Da_AM625_Laughing_Coyote_Board]         Board.org Debian Bullseye Xfce Image 2022-10-20]         /dev/mmcblk0bicDi:[Liboot/Shin]:[U-Boot SPL 2021.01-gf87208ea5764         /dev/mmcblk0b:[/boot/firmware/tiboot3.bin]:[U-Boot SPL 2021.01-gf87208ea5764         /dev/mmcblk0b:[/boot/firmware/tiboot3.bin]:[U-Boot SPL 2021.01-gf87208ea         /dev/mmcblk0b:[/boot/firmware/tiboot3.bin]:[U-Boot SPL 2021.01-gf87208ea         /dev/mmcblk0b:[/boot/firmware/tu-boot.img]:[U-Boot 2021.01-gf87208ea         /dev/mmcblk0 |

**Tip:** For debugging purposes you can either share the <code>beagle-version.txt</code> file you just downloaded using the steps shown in pictures above Or you can just paste the terminal output of sudo <code>beagle-version</code> to <code>https://pastebin.com/</code> and send us the link.

#### **Community resources**

Please execute the board diagnostics, review the hardware documentation, and consult the mailing list and IRC channel for support. BeagleBoard.org is a "community" project with free support only given to those who are willing to discussing their issues openly for the benefit of the entire community.

- Frequently Asked Questions

- Mailing List

- Live Chat

#### **Consulting and other resources**

Need timely response or contract resources because you are building a product?

Resources

#### Repairs

Repairs and replacements only provided on unmodified boards purchased via an authorized distributor within the first 90 days. All repaired board will have their flash reset to factory contents. For repairs and replacements, please contact support at BeagleBoard.org using the RMA form:

• RMA request

# **1.1.3 Understanding Your Beagle**

- Beagle 101

- Hardware

- Software

- Books

- PRU Cookbook

- BeagleBone Cookbook

- Exploring BeagleBone

- Bad to the Bone

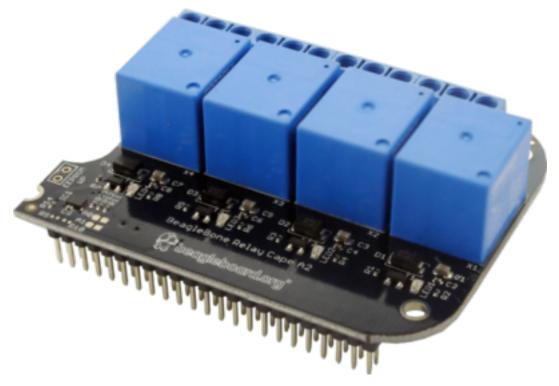

## 1.1.4 Working with Cape Add-on Boards

- Capes

- BeagleBone cape interface spec

- Accessories

# **1.2 Beagle 101**

Note: This page is under construction. Most of the information here is drastically out of date.

This is a collection of articles to aide in quickly understanding how to make use of Beagles running Linux. Most of the useful information has moved to *BeagleBone Cookbook*, but some articles are being built here from a different perspective.

Articles under construction or to be imported and updated:

- QWIIC, STEMMA and Grove Add-ons in Linux

- https://beagleboard.github.io/bone101/Support/bone101/

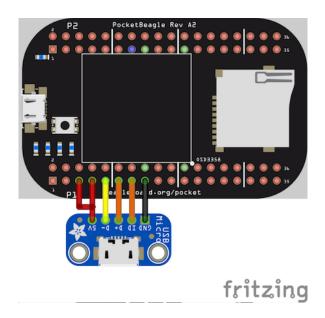

### 1.2.1 QWIIC, STEMMA and Grove Add-ons in Linux

**Note:** This article is under construction.

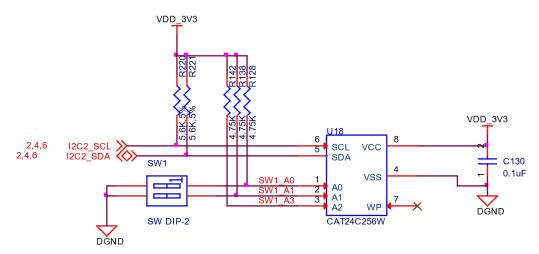

I'm creating a place for me to start taking notes on how to load drivers for I2C devices (mostly), but also other Grove add-ons.

For simplicity sake, I'll use these definitions

- add-on: the QWIIC, STEMMA (QT) or Grove add-on separate from your Linux computer

- device: the "smart" IC on the add-on to which we will interface from your Linux computer

- board: the Linux single board computer with the embedded interface controller you are using

- module: a kernel module that might contain the driver

#### **Using I2C with Linux drivers**

Linux has a ton of drivers for I2C devices. We just need a few parameters to load them.

Using a Linux I2C kernel driver module can be super simple, like in the below example for monitoring a digital light sensor.

```

cd /dev/bone/i2c/2

echo tsl2561 0x29 > new_device

watch -n0 cat "2-0029/iio:device0/in_illuminance0_input"

```

Once you issue this, your screen continuously refresh with luminance values from the add-on sensor.

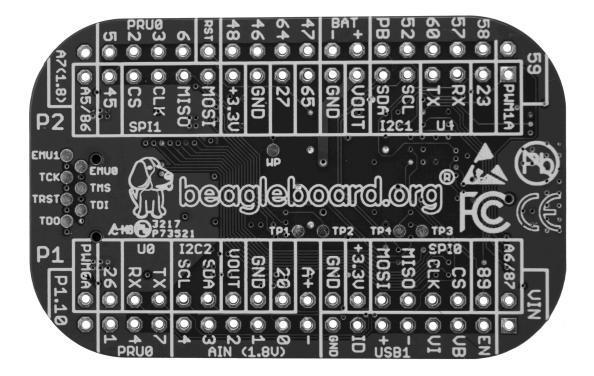

In the above example, /dev/bone/i2c/2 comes from which I2C controller we are using on the board and there are specific pins on the board where you can access it. On BeagleBone boards, there is often a symbolic link to the controller based upon the cape expansion header pins being used. See *I2C* for the cape expansion header pin assignments.

tsl2561 is the name of the driver we want to load and 0x29 is the address of the device on the I2C bus. If you want to know about I2C device addresses, the Sparkfun I2C tutorial isn't a bad place to start. The *new\_device* virtual file is documented in the Linux kernel documentation on instantiating I2C devices.

On the last line, watch is a program that will repeatedly run the command that follows. The *-n0* sets the refresh rate. The program cat will share the contents of the file *2-0029/iio:device0/in\_illuminance0\_input*.

2-0029/iio:device0/in\_illuminance0\_input is not a file on a disk, but output directly from the driver. The leading 2 in 2-0029 represents the I2C controller index. The 0029 represents the device I2C address. Most small sensor and actuator drivers will show up as Industrial I/O (IIO) devices. New IIO devices get incrementing indexes. In this case, *iio:device0* is the first IIO device driver loaded. Finally, *in\_illuminance0\_input* comes from the SYSFS application binary interface for this type of device, a light sensor. The Linux kernel ABI documentation for sysfs-bus-iio provides the definition of available data often provided by light sensor drivers.

| What: | /sys//iio:deviceX/in_illuminance_input     |

|-------|--------------------------------------------|

| What: | /sys//iio:deviceX/in_illuminance_raw       |

| What: | /sys//iio:deviceX/in_illuminanceY_input    |

| What: | /sys//iio:deviceX/in_illuminanceY_raw      |

| What: | /sys//iio:deviceX/in_illuminanceY_mean_raw |

| What: | /sys//iio:deviceX/in_illuminance_ir_raw    |

(continues on next page)

(continued from previous page)

Read further to discover how to find these bits of magic text used above.

The generic steps are fairly simple:

- 1. Identify driver name and address

- 2. Ensure driver is enabled in kernel build

- 3. Identify I2C signals on board and controller in Linux

- 4. Ensure pinmux set to I2C

- 5. Ensure add-on connection is good

- 6. Issue Linux command to load driver

- 7. Identify and utilize interface provided by driver

**Driver name** One resource that is very helpful is the list that Vaishnav put together for supporting Mikroelektronika Click add-ons. This list of Click add-ons with driver information can help a lot with matching a device to the driver name, device address, and kernel configuration setting.

**Note:** Documentation for your particular add-on might indicate a different device address than is configured on Click add-ons.

I'm not aware of a trivial way of discovering the mapping that Vaishnav created outside of looking at the kernel sources. As an example, let's look at the Grove Digital Light Sensor add-on which is documented to utilize a TSL2561.

Searching through the kernel sources, we can find the driver code at *drivers/iio/light/tsl2563.c*. There is a list of driver names in a i2c\_device\_id table:

```

static const struct i2c_device_id tsl2563_id[] = {

{ "tsl2560", 0 },

{ "tsl2561", 1 },

{ "tsl2562", 2 },

{ "tsl2563", 3 },

{};

```

**Important:** Don't miss that the driver, *ts*/2561, is actually part of a a superset driver, *ts*/2563. This can make things a bit trickier to find, so you have to look within the text of the driver source, not just the filenames.

#### **Kernel configuration**

#### **I2C signals and controller**

#### Pinmuxing

Wiring

Load driver

Interface

Finding I2C add-on modules \_\_\_\_\_\_\_ Note: There are some great resources out there:

- Adafruit list of I2C devices

- Sparkfun list of QWIIC devices

- Adafruit STEMMA QT introduction

**Pitfalls** Not all I2C devices with drivers in the Linux kernel can be loaded this way. The most common reason is that the device driver expects an interrupt signal or other GPIO along with the I2C communication. In these cases, a device tree overlay or driver modification may be necessary.

# **1.3 Contribution**

Note: This section is under developmement right now.

**Important:** First off, thanks for taking the time to think about contributing!

Note: For donations, see BeagleBoard.org - Donate.

The BeagleBoard.org Foundation maintains source for many open source projects.

Example projects suitable for first contributions:

- BeagleBoard project documentation

- Debian image bug repository

- Debian image builder

These guidelines are mostly suggestions, not hard-set rules. Use your best judgment, and feel free to propose changes to this document in a pull request.

## **1.3.1 Code of Conduct**

This project and everyone participating are governed by the same code of conduct.

Note: Check out https://forum.beagleboard.org/faq as a starting place for our code of conduct.

By participating, you are expected to uphold this code. Please report unacceptable behavior to contact one of our administrators or moderators on https://forum.beagleboard.org/about.

# **1.3.2 Frequently Asked Questions**

Please refer to the technical and contribution frequently asked questions pages before posting any of your own questions. Please feel encouraged to ask follow-up questions if any of the answers are not clear enough.

• Frequently asked questions contribution category on the BeagleBoard.org Forum

# **1.3.3** What should I know before I get started?

The more you know about Linux and contributing to upstream projects, the better, but this knowledge isn't strictly required. Simply reading about contributing to Linux and upstream projects can help build your vocabulary in a meaningful way to help out. Learn about the skills required for Linux contributions in the *Upstream Kernel Contributions* section.

The most useful thing to know is how to ask smart questions. Read about this in the *Getting support* section. If you ask smart questions on the issue trackers and forum, you'll be doing a lot to help us improve the designs and documentation.

#### Upstream Kernel Contributions

Note: For detailed information on Kernel Developmement checkout the official kernel.org kernel docs.

For a person or company who wishes to submit a change to the Linux kernel, the process can sometimes be daunting if you're not familiar with "the system." This text is a collection of suggestions which can help you get started and greatly increase the chances of your change being accepted.

**Note:** This version is an unofficial draft and is subject to change.

**Pre-requisites** The following are the skills that are needed before you actually start to contribute to the linux kernel:

- More Git!

- C-Programming

- Cross-arch Development

- Basics of embedded buses (I2C, UART, SPI, etc.)

- Device Drivers in Embedded Systems

- Device Trees

For more guidance, check out the Additional Resources.

**More Git!** It is highly recommended that you go through *Git Usage* before starting to read and follow these guidelines. You will need to have a proper git setup on your computer in order to effectively follow these steps.

**Creating your first patch** When you first enter the world of Linux Kernel development from a background in contributing over gitlab or github, the terminologies slightly change.

Your Pull Requests (PRs) now become Patches or Patch Series. You no longer just go to some website and click on a "Create Pull Request" button. Whatever code/changes you want to add will have to be sent as patches via emails.

As an example, let's consider a commit to add the git section to these docs. I stage these changes first using git add -p.

```

diff --git a/contribution/contribute.rst b/contribution/contribute.rst

index def100b..0af08c5 100644

--- a/contribution/contribute.rst

+++ b/contribution/contribute.rst

```

Then, commit the above changes.

**Note:** Don't forget to make your commit message descriptive of the feature you are adding or the work that you have done in that commit. The commit has to be self explanatory in itself. Link any references if you have used and paste any logs to prove your code works or if there is a fix.

```

git commit -vs

[linux-contrib 3bc0821] contribute.rst: Add git section

1 file changed, 27 insertions(+), 1 deletion(-)

```

Now, let's say we want to send this new feature to upstream kernel. You then have to create a patch file using the following command:

```

git format-patch -1 HEAD

0001-contribute.rst-Add-git-section.patch

```

This will generate one file that is generally referred to as the patch file. This is what you will now be sending upstream in order to get your patch merged. But wait, there are a few more things we need to setup for sending a patch via e-mail. That is, of course your email!

For configuring your email ID for sending patches refer to this excellent stackoverflow thread, configure gitsend-email.

Finally, after you have configured you email properly, you can send out a patch using:

git send-email 0001-contribute.rst-Add-git-section.patch

replacing of course the above patchfile name with whatever was your own patch. This command will then ask you To whom should the emails be sent (if anyone)? Here, you have to write the email address of the list you want to send out the patch to.

git send-email also has command line options like --to and --cc that you can also use to add more email addresses of whoever you want to keep in CC. Generally it is a good idea to keep yourself in CC.

**C-Programming** It is highly recommended that you have proficiency in C-Programming, because well the kernel is mostly written in C! For starters, you can go through Dennis Ritchie's C Programming book to understand the language and also solve the exercises given there for getting hands on.

**Cross-arch Development** While working with the kernel, you'll most likely not be compiling it on the machine that you intend to actually boot it on. For example if you are compiling the Kernel for BeageBone Black it's probably not ideal for you to actually clone the entire kernel on BeagleBone Black and then compile it there. What you'd do instead is pick a much powerful machine like a Desktop PC or laptop and then use cross arch compilers like the arm-gcc for instance to compile the kernel for your target device.

**Basics of embedded buses (I2C, UART, SPI, etc.)** In the world of embedded, you often need to communicate with peripherals over very low level protocols. To name a few, I2C, UART, SPI, etc. are all serial protocols used to communicate with a variety of devices and peripherals.

It's recommended to understand at least the basics of each of the protocol so you know what's actually going on when you write for instance an I2C or SPI driver to communicate with let's say a sensor. **Device Drivers in Embedded Systems** I used the term "Drivers" in the above section, but what does it really mean?

Why "device" drivers?

TODO

Why do we need drivers?

TODO

What do drivers look like?

TODO

**Device Trees** We just learned about drivers, and it's time that once you have written a driver in the kernel, you obviously want it to work! So how do we really tell the kernel which drivers to load? How do we, at boot time, instruct which devices are present on the board you are booting on?

The kernel does not contain the description of the hardware, it is located in a separate binary: the device tree blob.

#### What is a Device Tree?

A device tree is used to describe system hardware. A boot program loads a device tree into a client program's memory and passes a pointer to the device tree to the client.

A device tree is a tree data structure with nodes that describe the physical devices in a system.

#### **Additional Resources**

- 1. Device Trees for Dummies PDF

- 2. What are Device Drivers

- 3. Submitting your patches upstream

### **1.3.4** How can I contribute?

The most obvious way to contribute is using the git.beagleboard.org Gitlab server to report bugs, suggest enhancements and providing merge requests, also called pull requests, the provide fixes to software, hardware designs and documentation.

#### **Reporting bugs**

Suggesting enhancements

Submitting merge requests

### 1.3.5 Style and usage guidelines

- Git Usage

- Git commit messages

- Documentation Style Guide

#### **Git Usage**

**Note:** For detailed information on Git and Gitlab checkout the official Git and GitLab help page. Also, for good GitLab workflow you can checkout the Introduction to GitLab Flow (FREE) page.

These are (draft) general guidelines taken from BioPython project to be used for BeagleBoard development using git. We're still working on the finer details.

This document is meant as an outline of the way BeagleBoard projects are developed. It should include all essential technical information as well as typical procedures and usage scenarios. It should be helpful for core developers, potential code contributors, testers and everybody interested in BeagleBoard code.

**Note:** This version is an unofficial draft and is subject to change.

**Relevance** This page is about actually using git for tracking changes.